第四章 处理器

在本章中, 我们将讨论现代计算机中央处理器的组成以及工作方式, 我们会从单周期CPU开始, 逐步扩展到现代的流水线CPU.

序言: 计算机抽象

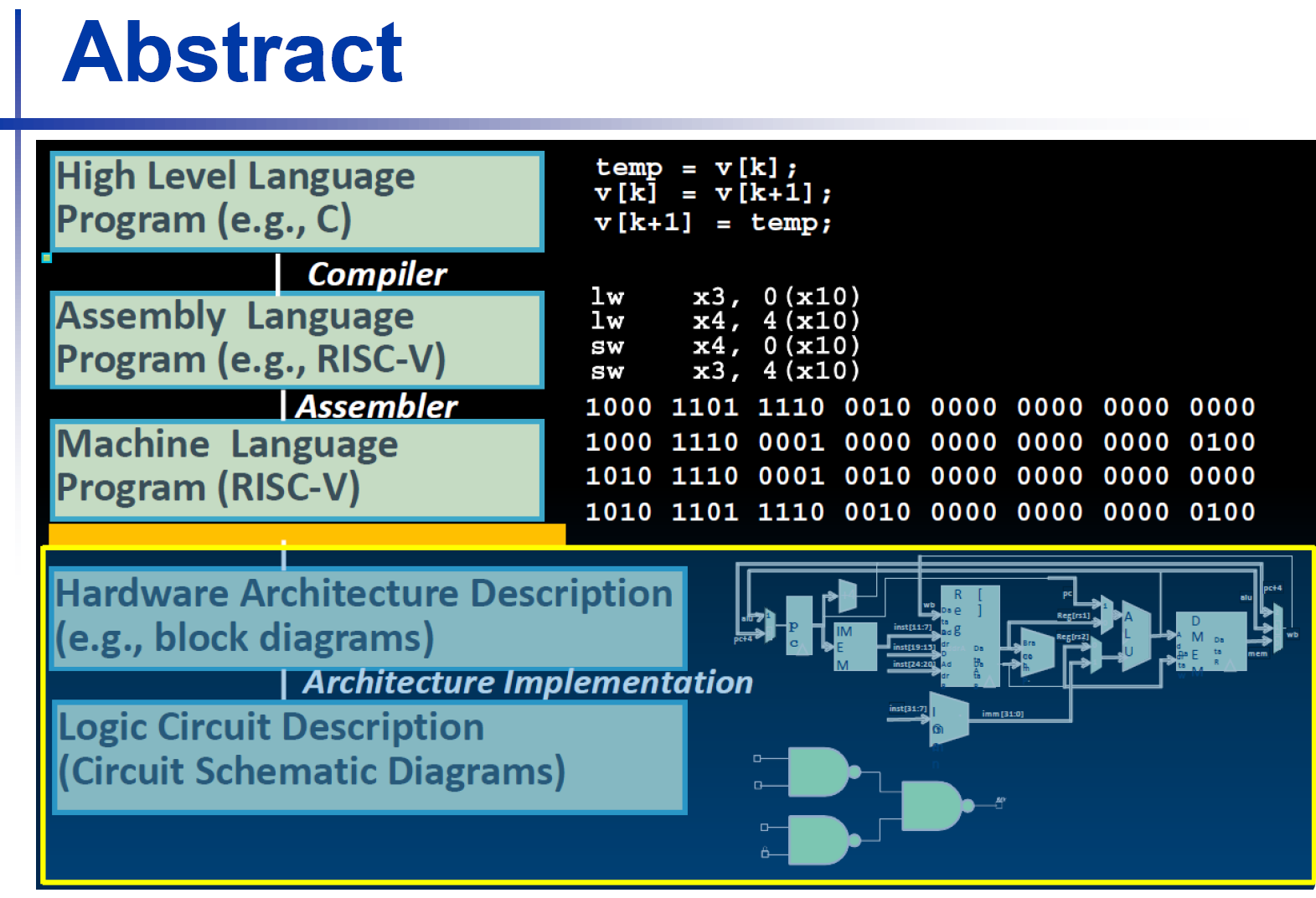

在计算机系统中, 我们编写的高级语言程序(High Level Language Program)被编译器编译为汇编代码(Assembly Language), 再由汇编器翻译为机器语言(Machine Language). 机器语言被CPU中的硬件架构处理, 而这些架构又是由一个个逻辑门电路组成的.

在第三章中, 我们已经讨论了门电路是如何组成ALU(Arithmetic Logical Unit)等原件的. 在本章中, 我们会聚焦于CPU是如何通过这些抽象的元件进行组合, 完成译码, 存取数据等一系列操作的.

CPU Overview

单核处理器的基本组成

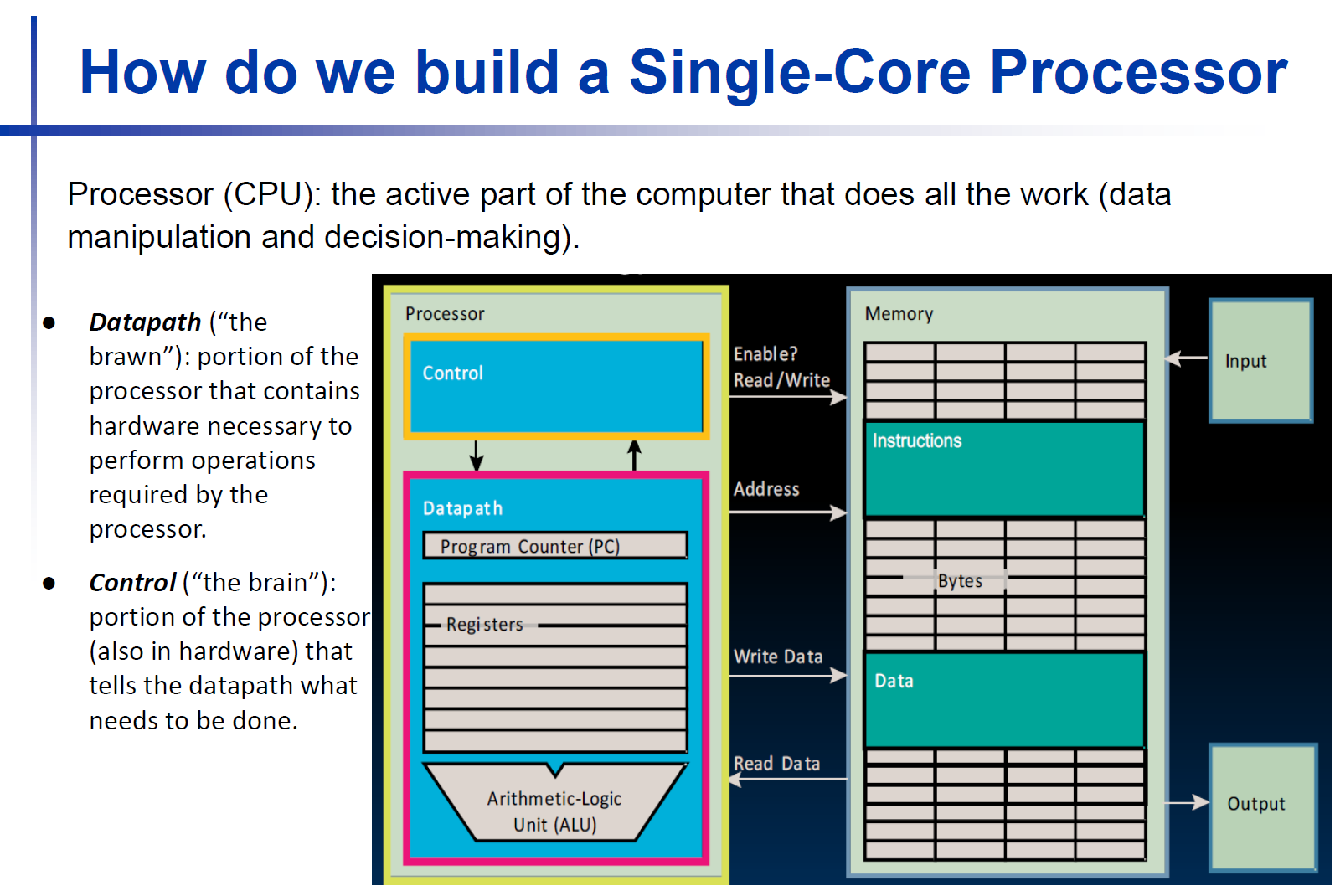

一个单核处理器包含数据通路和控制通路两部分.

数据通路是负责处理和传输数据的硬件集合, 其主要包括:

- 寄存器文件 (Register File, RF)

- 主内存 (Main Memory)

- 算数逻辑单元 (ALU)

- 立即数生成器 (Immediate generator)

而控制通路是负责产生时序和控制信号的硬件集合, 主要包括:

- 主控制单元 (Main Control Unit)

ALU控制单元(ALU Control Unit)

稍后我们会详细讨论这些硬件是如何组成CPU的.

CPU处理指令的基本流程

-

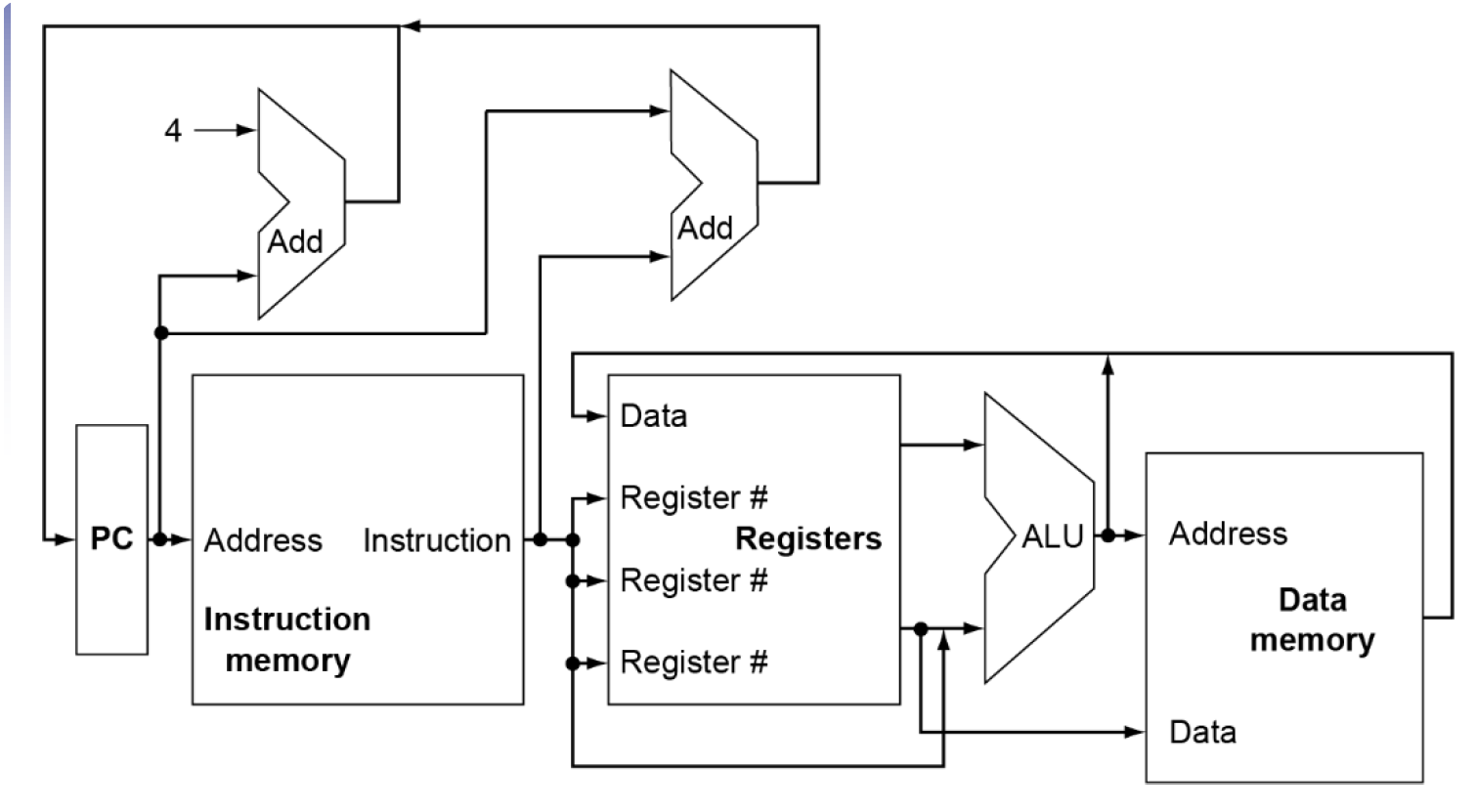

指令内存(Instruction Memory)从PC中取出指令地址, 将指令送往不同的其他硬件:

- 寄存器文件

- ALU

-

寄存器文件读取寄存器的值

-

ALU进行计算, 这里的计算主要分为以下几种类型

-

对

R-type或I-type指令进行的算数运算 -

对

J-type或B-type指令进行的跳转地址计算 -

对访存指令进行的访存地址计算

-

-

读取内存/写入内存

-

写入寄存器文件

-

更新PC

控制信号

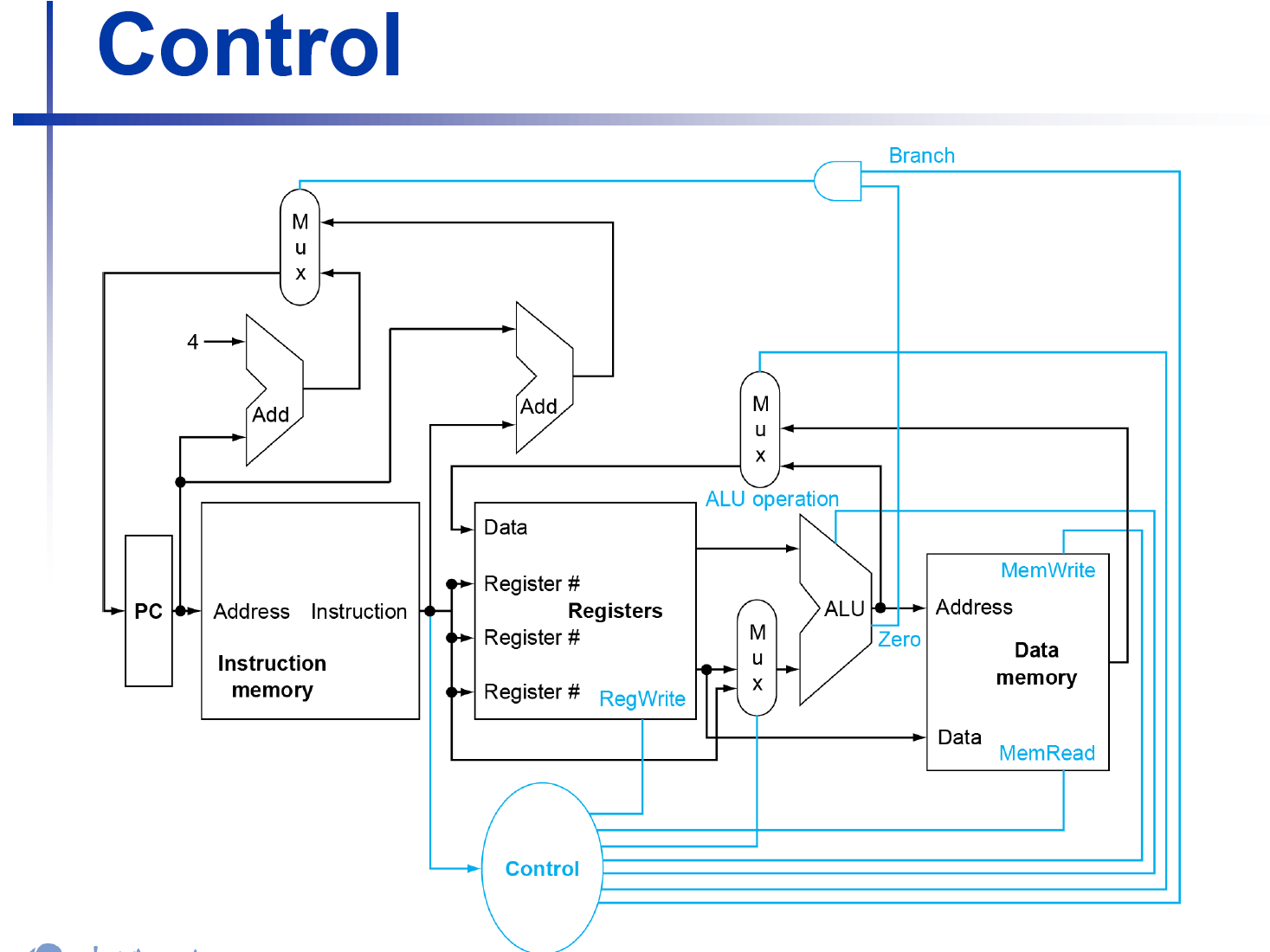

除了数据通路外, 还有大量控制信号控制CPU的行为. 其主要包括:

RegWrite(控制是否写寄存器)Memread(是否读内存)Memwrite(是否写内存)Zero(ALU计算的值是否为0)ALUop(用于控制ALU进行的运算类型)

我们后续会详细关注这些指令的用途和实现.

时序逻辑

逻辑设计基础

在逻辑电路中:

-

数据用电压的高低表示, 低电平表示0, 高电平表示1.

-

每一条线路表示一个比特.

-

多比特的数据由多条线路组成的 总线 (Bus)传输.

组合逻辑与时序逻辑:

- 每个组合逻辑电路相当于一个函数, 输出是输入的函数.

- 时序逻辑电路储存输入的值.

组合电路主要包含 ALU, Adder, Mux, 与门, 或门等. 我们这里主要讨论时序逻辑.

时序元件

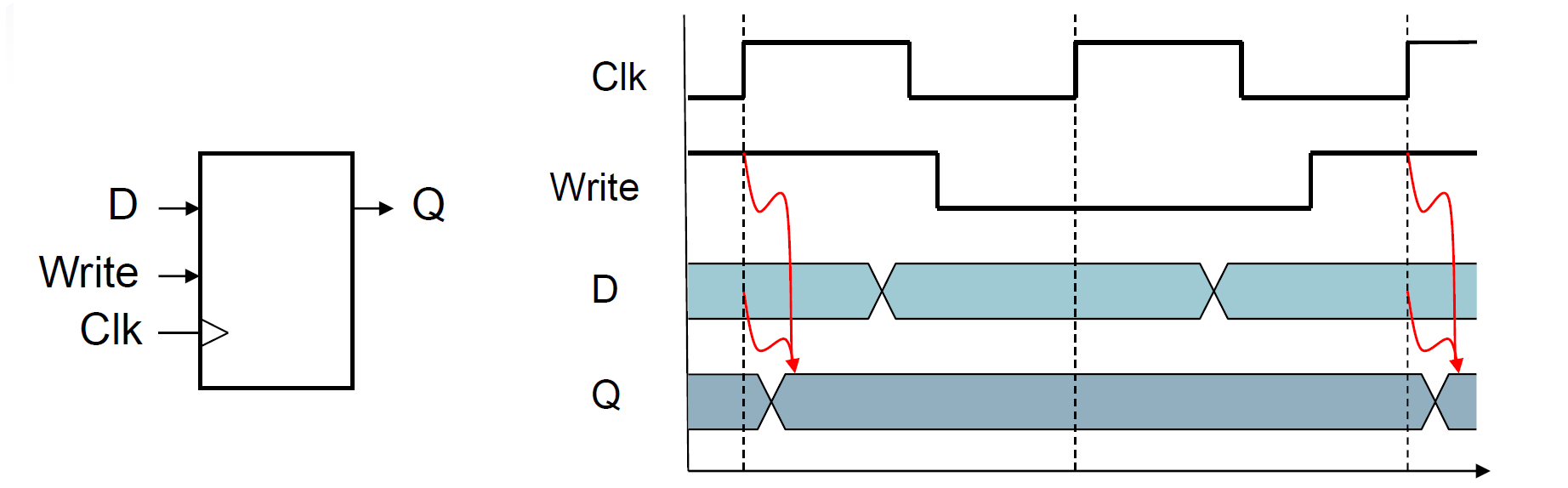

寄存器是一个时序逻辑元件.

在时钟上升沿, 寄存器检查输入端D的值, 并且判断Write 信号是否为True, 当输入信号发生改变, 且Write 信号为真时, 寄存器的值发生改变.

而在每一个时钟周期内部, 组合逻辑操纵数据. 数据从一个状态元件前往另一个状态元件. 这个过程不涉及改变任何时序逻辑元件的输出.

而时钟周期的长度由组合逻辑中最长的线路决定.

单周期处理器设计

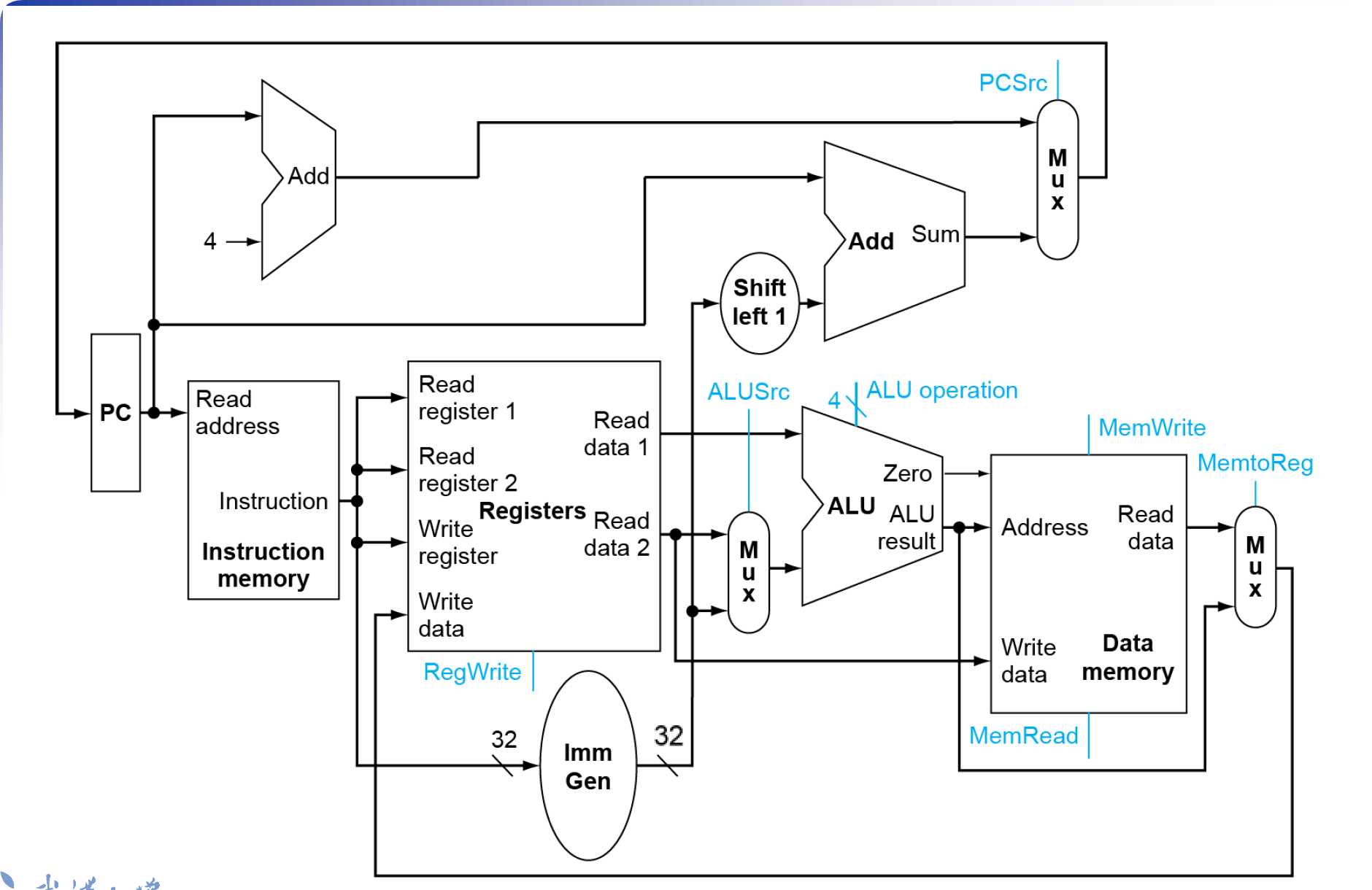

数据通路(Datapath)

这个部分中, 我们会通过以下几个步骤, 一步步搭建出一个简单处理器的数据通路.

- 取指 (Instruction Fetch)

- R-type

- B-type

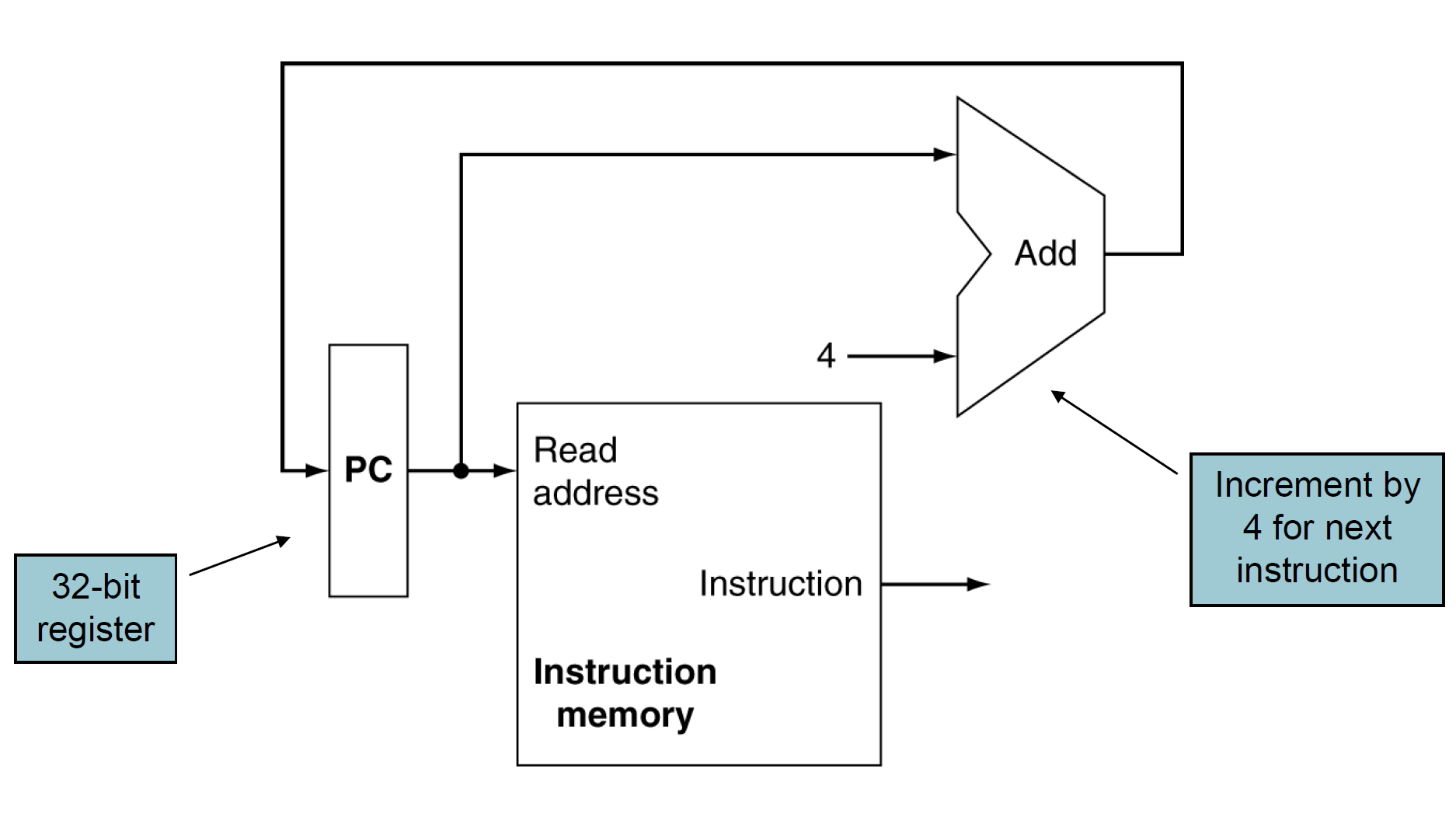

取指

时钟上升沿, PC接收Add 送来的数据, 并且更新输出端的数据, 将新的PC值同时送往:

Add- 指令内存(Instruction Memory)

指令内存是一个组合电路, 在接收PC的值后经过一个较短的延迟, 输出稳定为本次要执行的指令.

R-type

R-format 指令具有以下特征:

- 读两个寄存器值作为输入

ALU进行算数/逻辑运算- 将计算的结果存入寄存器文件 (Register File, RF)

因此, 我们将以下组合元件加入CPU:

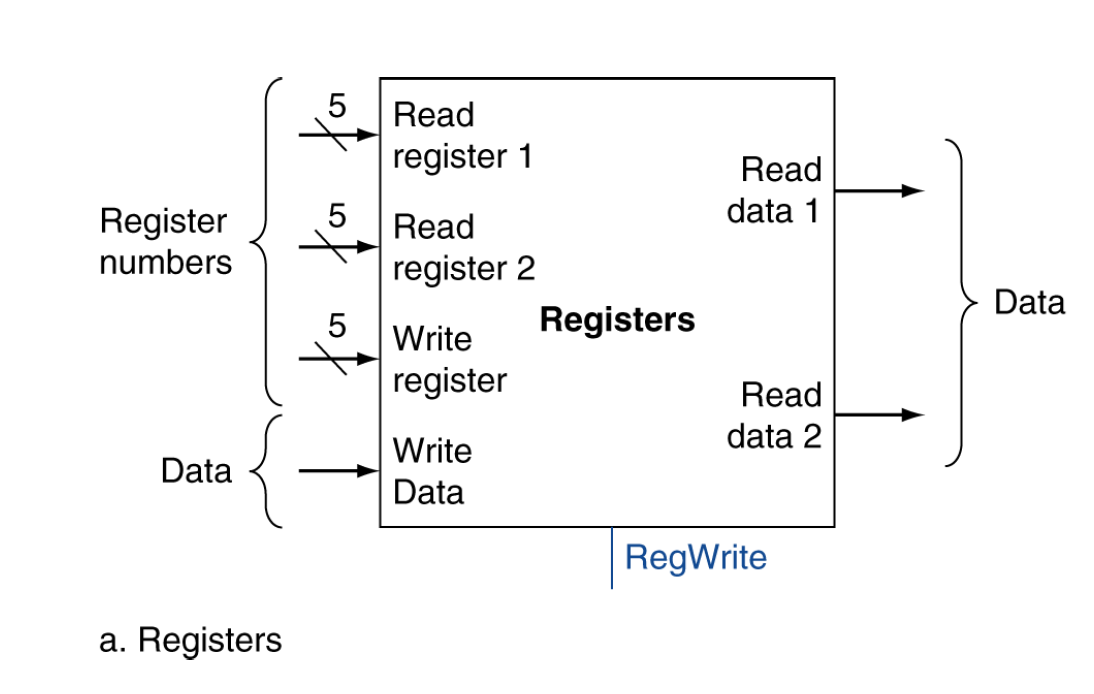

Registers

寄存器从指令内存接受输入, 包括:

- Read register 1 / 2

- Write register

Opcode,RegWrite等控制信号

并且给出输出:

- Read data 1/2

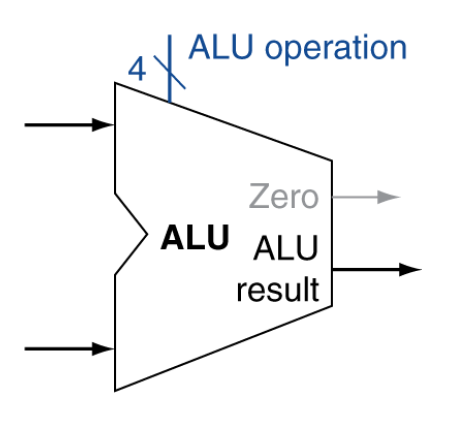

ALU

接受 Immediate 或 Read data, 通过 ALU op 控制行为进行输出.

输出包括:

- Zero, 表示计算结果是否为0

- ALU result, 计算结果.

Load/Store Instructions

在此类指令中, 我们有了计算立即数地址的需求, 因此引入新的组合元件 ImmGen

其以完整的32位指令作为输入, 以扩展(符号扩展或逻辑扩展, 取决于指令类型)后的立即数作为输出.

在输入指令无立即数需求时, 其输出通常为全0

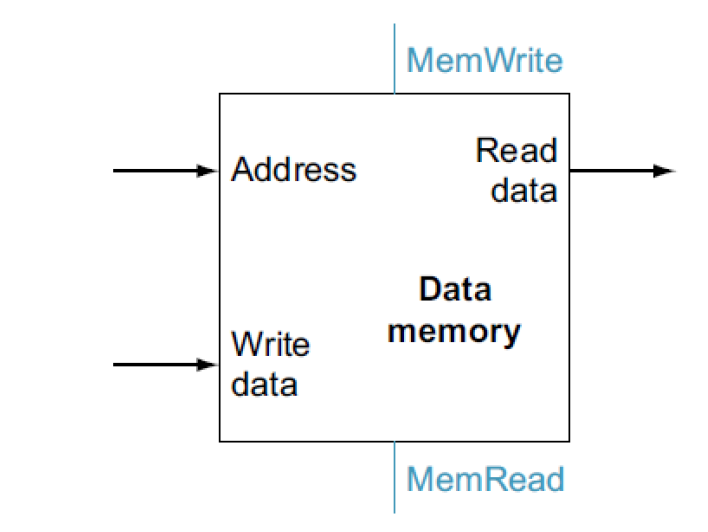

以及组合元件 数据内存

其 Address 由ALU 计算而来.

处理完几类主要的datapath 后, 得到的Full Datapath 如图所示.

控制通路(control path)

ALU Control

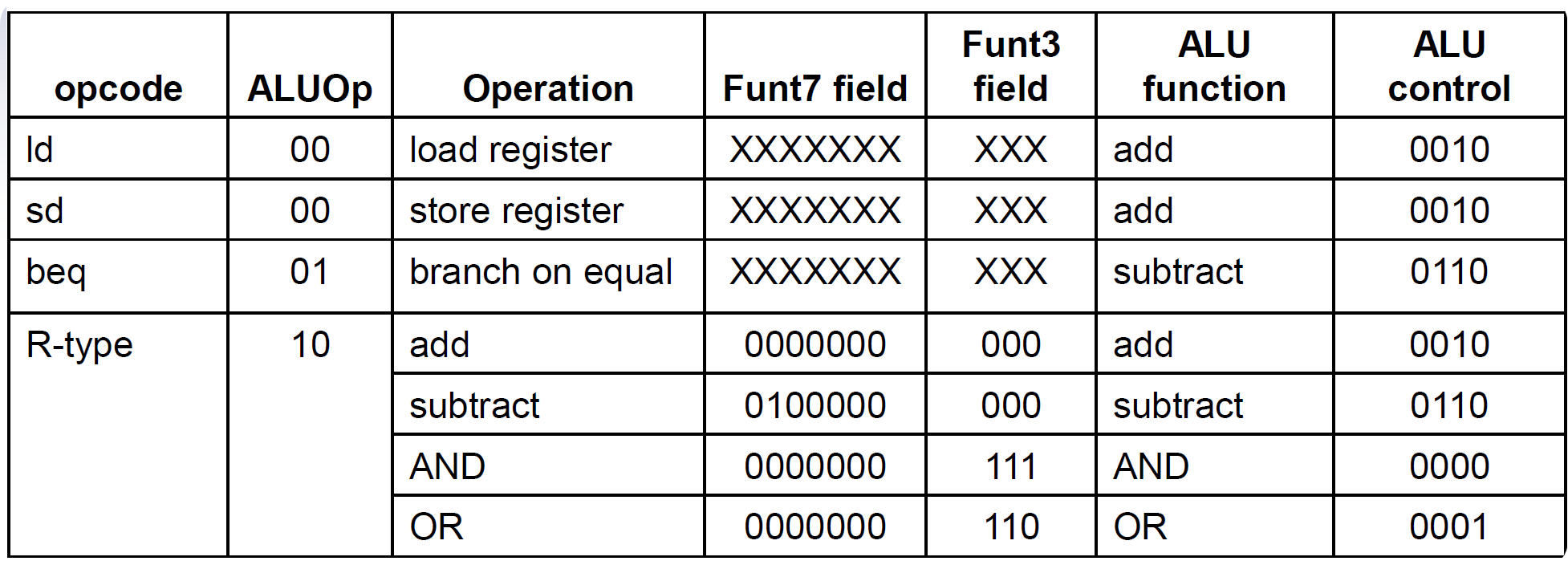

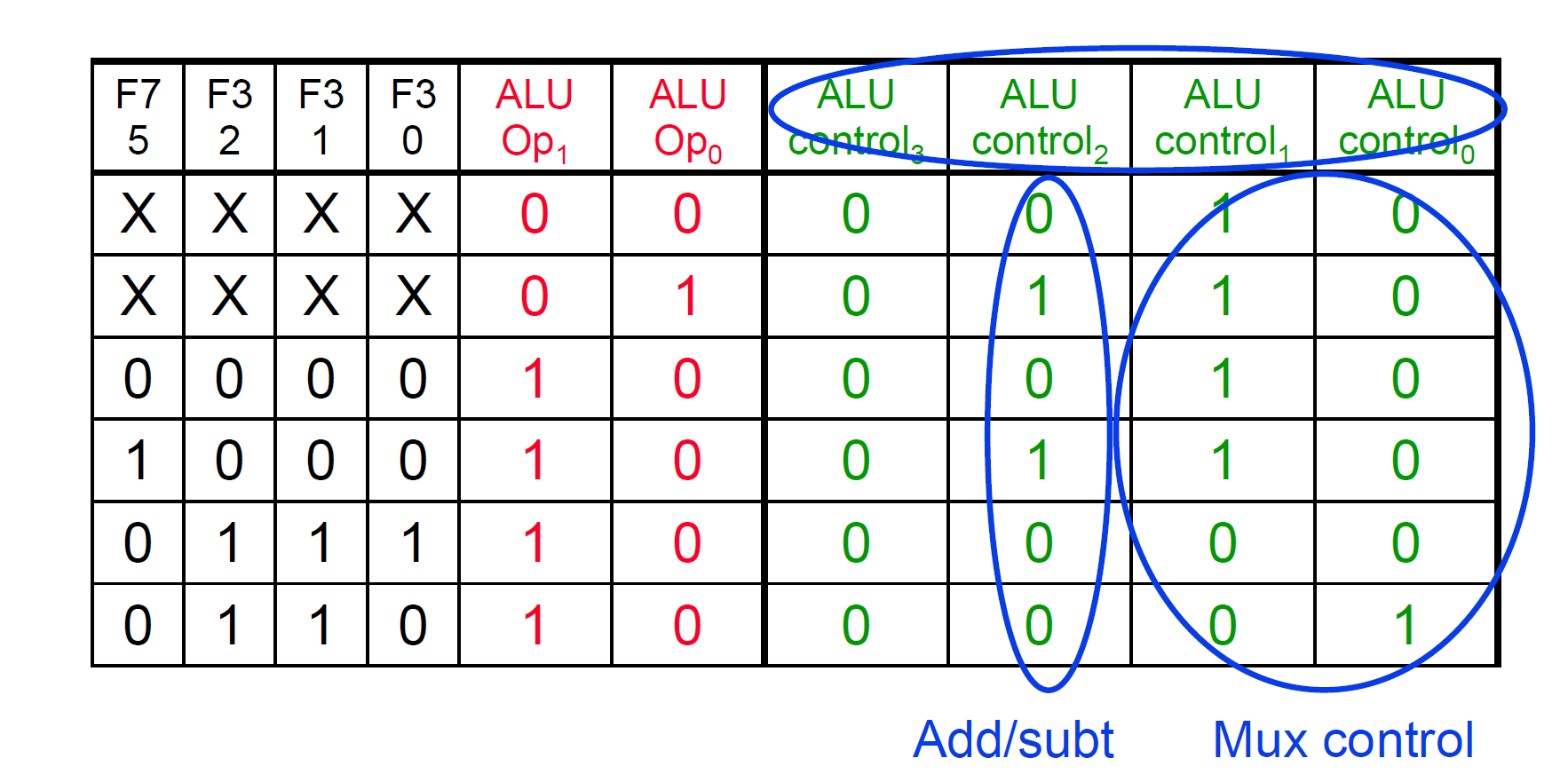

ALUop是从opcode 中取出的两位ALU控制码, 其用于生成ALU control, 用于决定ALU的 运算类型.

-

ALU op为00时, 表示操作类型为ld或sd执行加法,ALU control为0010 -

ALU op为01时, 表示操作类型为branch on equal(B-type), 执行减法,ALU control为0110. -

ALU op为10时, 表示操作类型为R-type, 继续由Funt3和Funt7确定具体的ALU control.其具体的真值表为:

多重控制信号

一般而言, 单周期CPU中的控制信号有:

-

ALUSrc(ALU Source), 用于决定ALU的第二个输入是来自:- 若其为0: 寄存器文件, 用于执行

R-format指令 - 若其为1: 立即数, 用于执行

S-format,I-format,B-format指令等.

- 若其为0: 寄存器文件, 用于执行

-

MemtoReg决定RegWrite的入口, 是从内存中读取的数据还是ALU的计算结果 -

Branch与Zero这两个信号通常连接到一个与门的两个输入端, 用于决定PCSrc.

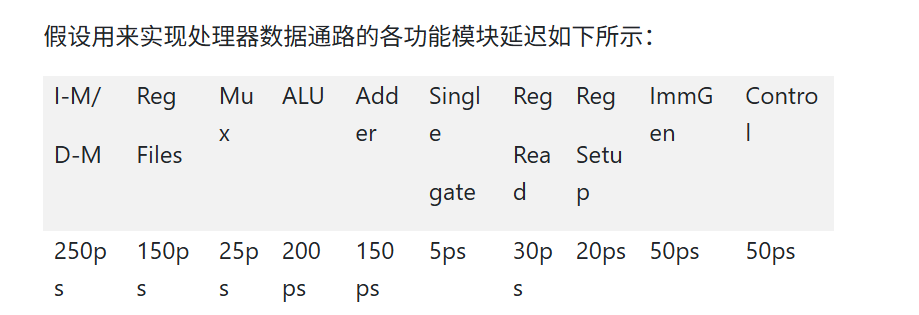

路径延迟

计算CPU执行某种类型的指令的延迟, 必须确定数据通路中最长的一条的长度.

以 R-type 为例:

-

最长数据通路为

PC -> IM -> RF -> rs2 -> MUX1 -> ALU -> MUX2->writeData -

如果要计算延迟, 即PC输出稳定至

writeData输入稳定, 即250 + 150 + 200 + 25 + 25 = 700ps -

如果要计算周期长度, 那么还要加上50ps的寄存器搭建和读取时间.